Elektrotech. Inftech. https://doi.org/10.1007/s00502-025-01318-0

# Performance review of state-of-the-art 1.2 kV SiC devices based on experimental figures-of-merit

Takanobu Ohno · Michael Haider · Spasoje Mirić

Received: 28 December 2024 / Accepted: 24 February 2025 © The Author(s) 2025

Abstract Power electronic systems, such as photovoltaic inverters and drive systems, increasingly use wide bandgap semiconductors like Gallium Nitride and Silicon Carbide (SiC). With SiC devices widely available, many are packaged in TO-247-4 and offer comparable on-state resistances and blocking voltages. However, supply shortages raise the question of whether devices from different manufacturers can be interchanged without design changes. This paper analyzes SiC devices from multiple manufacturers using empirical measurements in a bridge-leg configuration at voltages up to 950 V and temperatures up to 150°C. Charge independence over junction temperature is quantified, and measurement-based Figures of Merit (FOMs) are compared. Results show similar performance in hard-switched converters with minimal overlap losses. However, in soft-switching applications, the first device achieves 1.5 times better FOM, while in high-current scenarios with significant overlap losses, the third device excels with a FOM nearly three times higher. These findings are further validated by dv/dt measurements.

**Keywords** Silicon carbide (SiC) devices  $\cdot$  1.2 kV power devices  $\cdot$  Measurement-based figures-of-merit  $\cdot$  High-temperature

## Leistungsbewertung modernster 1,2-kV-SiC-Bauelemente basierend auf experimentellen Figures-of-Merit

**Zusammenfassung** Leistungselektronische Systeme wie Photovoltaik-Wechselrichter und Antriebssysteme

T. Ohno  $\cdot$  M. Haider  $\cdot$  S. Mirić ( $\boxtimes$ ) Institute for Mechatronics, University of Innsbruck, Technikerstraße, 6020 Innsbruck, Tirol, Österreich spasoje.miric@uibk.ac.at

setzen zunehmend auf Wide Bandgap-Halbleiter wie Galliumnitrid und Siliziumkarbid (SiC). Mit der breiten Verfügbarkeit von SiC-Bauelementen sind viele in TO-247-4-Gehäusen erhältlich und bieten vergleichbare Durchlasswiderstände sowie Sperrspannungen. Allerdings werfen Lieferengpässe die Frage auf, ob Bauelemente verschiedener Hersteller ohne Designanpassungen austauschbar sind. Diese Arbeit analysiert SiC-Bauelemente mehrerer Hersteller anhand empirischer Messungen in einer Halbbrückenkonfiguration bei Spannungen bis zu 950V und Temperaturen bis zu 150°C. Die Ladungsunabhängigkeit über die Sperrschichttemperatur wird quantifiziert, und messbasierte Figures of Merit (FOMs) werden verglichen. Die Ergebnisse zeigen eine ähnliche Leistung in hart geschalteten Wandlern mit minimalen Überlappungsverlusten. In weich schaltenden Anwendungen erreicht jedoch das erste Bauelement einen 1,5-fach besseren FOM, während das dritte Bauelement in Hochstromszenarien mit erheblichen Überlappungsverlusten durch einen nahezu dreifach höheren FOM herausragt. Diese Erkenntnisse werden durch dv/dt-Messungen weiter validiert.

$\begin{tabular}{ll} Schlüsselwörter & Siliciumkarbid (SiC)-Bauelemente \cdot 1,2-kV-Leistungsbauelemente \cdot Messbasierte \\ Gütemaße \cdot Hochtemperatur \\ \end{tabular}$

#### 1 Introduction

Modern switched-mode power electronic converter systems increasingly incorporate wide bandgap (WBG) power semiconductors to augment the efficiency of power conversion processes. Gallium Nitride (GaN) and Silicon Carbide (SiC) are the prominent WBG semiconductor materials used in state-of-the-art power converter systems. GaN is favored for 450 V [1] DC-link voltage applications, while SiC is the ma-

Fig. 1 The projected growth of the U.S. SiC semiconductor devices market from 2020 to 2030, measured in U.S. dollars (millions). The forecast suggests a diverse expansion across all categories, reflecting the increasing adoption of SiC devices in various applications, see [25]

terial favored for power electronic systems operating at voltages above  $500\,\mathrm{V}$  [2].

The exceptional performance attributes of SiC [3, 4], facilitate the realization of power electronic converter systems with enhanced efficiency and increased power density, making them particularly advantageous for grid-tied systems or those supplied by high-voltage batteries [5, 6]. Typical examples of such applications range between several kilo-watts up to several tens of kilo-watts, such as photovoltaic (PV) inverters [7, 8], power factor correction (PFC) rectifier systems in the telecommunication sector for supplying, e.g., data centers [9, 10], advanced industrial drive systems [11, 12], integrated (onboard) chargers for electric vehicles (EVs) [13–15], and EV propulsion systems [16], to mention a few.

Adopting WBG devices in a specific application can be economically justified by their lower loss characteristics compared to silicon devices [17]. For instance, integrating SiC devices within the inverter of an EV motor drive system significantly influences the entire powertrain. This is primarily because their reduced losses lead to lower heat generation, enabling a downsizing of the cooling system. Such a reduction decreases the EV's overall weight and facilitates an extended driving range. Alternatively, if the desired range is maintained, it allows for a smaller battery pack. Ultimately, this cascades into a tangible reduction in the vehicle's weight and the costs associated with cooling and battery systems. This cost-efficiency can offset the initial higher investment in SiC devices, making them a financially viable option in the long term [18, 19].

In light of the projected surge in demand for EVs, grid storage systems, and PV inverters [20–24], SiC

Tab. 1 FOMs from literature linked to power dissipation characteristics of the switching devices

| Name/Symbol        | Analytic Expression                  | Based on Literature References |  |  |  |

|--------------------|--------------------------------------|--------------------------------|--|--|--|

| FOMI               | $\frac{1}{R_{\rm ds,on}Q_{\rm oss}}$ | [34]                           |  |  |  |

| FOM <sub>II</sub>  | $\frac{1}{R_{ m ds,on}Q_{ m g0}}$    | [35]                           |  |  |  |

| FOM <sub>III</sub> | $\frac{1}{R_{\rm ds.on}Q_{\rm M}}$   | [36]                           |  |  |  |

devices are predicted to have exponential market growth, as illustrated in Fig. 1. This growing demand presents a substantial business opportunity, prompting an increasing number of manufacturers to enter the SiC power semiconductor market. Consequently, the market's expansion has underscored the necessity for rigorous characterization and comparison of devices from various manufacturers. Such analyses are vital for power electronics engineers, simplifying the decision-making process in selecting appropriate devices for their projects. Determining whether performance differences exist among SiC devices from different manufacturers is crucial, as identifying uniformity in performance would facilitate second sourcing without additional design complexities. Conversely, if variances are present, it becomes imperative to quantify these differences and evaluate their impact on converter performance.

For the comparison of the devices, we use Figure of Merit (FOM) listed in Tab. 1, which were initially introduced for evaluating the material properties essential to the functionality of devices, encompassing critical electric field, electron mobility, and thermal conductivity [26–29]. Semiconductor device development aims to improve the trade-off relationship among onresistance, parasitic capacitances, breakdown voltage, and short-circuit withstand time [30]. For 1.2kV SiC devices, optimization studies of cell layout, JFET regions, and P-well regions have been conducted using FOMs as performance indicators [31–33].

These foundational FOMs, when integrated with advancements in manufacturing processes and packaging techniques, evolved into what we refer to as diearea-independent device FOMs. Such FOMs encapsulate higher-level device parameters, including onstate resistance  $R_{ds,on}$ , output charge  $Q_{oss}$ , gate charge  $Q_{\rm g}$  or Miller charge  $Q_{\rm M}$ , providing a comprehensive framework for comparison across different technologies, manufacturers, or breakdown voltages. To ensure a fair comparison of devices from different manufacturers, relying on FOMs derived from experimentally obtained data rather than datasheet specifications is essential. This approach mitigates the potential bias wherein manufacturers may present their devices in an overly favorable light, which might not reflect their actual performance in practical applications. Thus, in this paper, we estimate the FOMs based on measured data, which offer a genuine perspective on the device's performance, enabling a more accurate and reliable assessment. It should be noted that this method is not officially certified or licensed, but similar approaches are being used for device characterization [37, 38], and the used equipments are certified.

#### 2 Experimental setup

This section introduces the hardware demonstrator and the employed high-temperature measurement

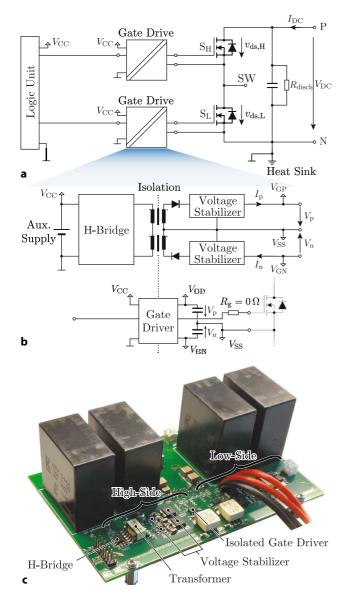

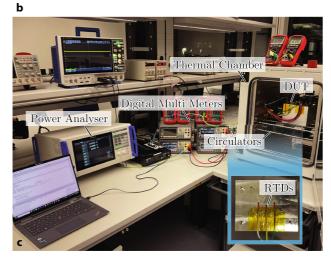

Fig. 2 (a) Schematic of the hardware demonstrators designed to evaluate the Figure of Merit (FOM) of considered power semiconductors  $S_{\rm H}$  and  $S_{\rm L}$ . (b) Schematic of the gate drive circuit, including the voltage stabilizers, to ensure constant gate drive voltage levels of  $V_{\rm p}=15\,\rm V$  and  $V_{\rm n}=-3.8\,\rm V$  across characterization. Indicated terminals are used to measure the gate drive voltages and currents. (c) Hardware demonstrator of the assembled half-bridge

setup to characterize the FOMs of the device-undertest (DUT).

#### 2.1 Half-bridge hardware demonstrator

The details of the designed hardware demonstrator rated for a DC-link voltage up to  $950\,\mathrm{V}$  and an ambient temperature of up to  $150\,^\circ\mathrm{C}$  are shown in Fig. 2. The demonstrator is designed to employ two TO-247-4 power transistors (S<sub>H</sub> and S<sub>L</sub>, cf. Fig. 2a) positioned close to each other to minimize the commutation loop and securely mounted onto a heatsink using a thermal

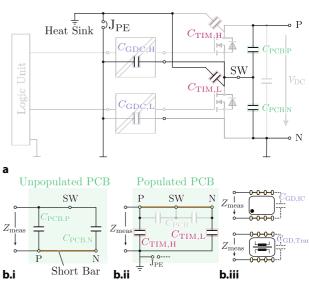

Fig. 3 (a) Schematic highlighting contributions to the parasitic switch-node capacitance  $C_{\rm par}$  in the employed hardware demonstrator.  $C_{\rm PCB,P}$  and  $C_{\rm PCB,N}$  denote the parasitically formed capacitances between PCB tracks,  $C_{\rm TIM,H}$  and  $C_{\rm TIM,L}$  the drain tab of high- and low-side switching devices to heat sink capacitance, and  $C_{\rm GDC,H}$  and  $C_{\rm GDC,L}$  the parasitic capacitances introduced by the gate drive circuit for high- and low-side switching devices. (b) Equivalent circuits for various impedance measurements to determine the parasitic capacitances. (c) Impedance measurement results that are used to deduce the values of the parasitic capacitances in (1)

interface material (TIM) that ensures effective thermal conduction and provides the necessary electrical insulation.

The identical layout of the isolated gate drive circuits ensures equivalent performance for low- and high-side power transistors. The gate resistor was chosen with  $R_g = 0 \Omega$  to benchmark the limit of the device, i.e., maximum dv/dt values [12]. However, it should be noted that the measured on-state resistance, gate charge, and output charge are independent of the gate resistor. Furthermore, in industrial applications typically employ a non-zero gate resistor [39, 40]. The gate driver IC [41] operates at a positive gate voltage of  $V_p = +15$ V for turn on and a negative gate voltage  $V_{\rm n} = -3.8 \, \rm V$  for turn off, ensuring to stay within the safe-operating-area (SOA) for all evaluated MOSFETs. Stable gate drive voltages are ensured by a voltage stabilizer, containing a voltage tracker [42] with its output voltages referenced by a low dropout (LDO) voltage regulator, within the positive and negative supply rail as shown in Fig. 2b. This approach is essential to operate the DUT at consistent voltage levels across varying switching frequencies, i.e., varying gate driver power demands. With a specified power of 3 W, the gate drive circuit can handle the power transistors at switching frequencies as high as  $f_{\rm sw} = 1\,{\rm MHz}$ . This high  $f_{\rm sw}$  capability is crucial for accurately measuring the output charge  $Q_{\rm oss}$  at lower DC-link voltages.

The assembled hardware demonstrator is shown in Fig. 2c, indicating terminals within the low-side gate drive circuit used to measure the gate drive DC voltages  $V_{\rm p}$ ,  $V_{\rm n}$  and gate drive DC currents  $I_{\rm p}$ ,  $I_{\rm n}$  (cf. Fig. 2b). These quantities allow the derivation of the gate drive power within operation, as needed to characterize the gate charge  $Q_{\rm g}$  and later to obtain the Miller charge  $Q_{\rm M}$ .

To characterize the output charge  $Q_{\rm oss}$  by zero-current switching (ZCS) experiments, it is crucial to quantify the parasitic switch-node capacitance  $C_{\rm par}$  arising from the actual construction of the hardware demonstrator. The total (parasitic) switch-node capacitance  $C_{\rm par}$  includes the capacitance  $C_{\rm PCB}$  resulting from the PCB layout, the capacitance formed between the heat sink and the drain pad insulated by TIM  $C_{\rm TIM} = C_{\rm TIM,H} = C_{\rm TIM,L}$  and the capacitance associated with the gate drive circuit  $C_{\rm GDC} = C_{\rm GDC,H} = C_{\rm GDC,L}$  as also shown in Fig. 3a.

$C_{PCB,P}$  and  $C_{PCB,N}$  are identified as the capacitance between the switch-node SW and the DC bus, represented by either the positive or the negative DClink rail P or N. To measure  $C_{PCB}$ , one must short the DC-link rails on the PCB when no components are present, which equivalently results in total  $C_{PCB}$  =  $C_{PCB,P} + C_{PCB,N}$  that will be seen in the measurement, see Fig. 3b.i. Using an impedance analyzer on the switch-node SW and the shorted P-N terminal, we can deduce from the impedance measurement that  $C_{PCB} = 123 \,\mathrm{pF}$ , see Fig. 3c. Furthermore,  $C_{TIM,H}$  and  $C_{\text{TIM,L}}$ , established by the TIM employed on high- and low-side switching devices, can be measured by shorting the DC-link rails to the switch node on a component-populated PCB mounted on the heatsink. Ensuring the heatsink's protective earth (PE) jumper is open, see Fig. 3b.ii, the measured capacitance between P-N-SW and heatsink measures  $C_{\text{TIM},H} + C_{\text{TIM},L} =$ 43 pF, see Fig. 3c. Due to symmetry, we assume TIM capacitances are equal, resulting in  $C_{\text{TIM,H}} = C_{\text{TIM,L}} =$ 21.5 pF. The isolation requirement of the gate drive components, specifically the gate driver IC and the transformer, cause  $C_{GDC} = C_{GDC,Trans} + C_{GDC,IC}$ . When measured separately with an impedance analyzer, see Fig. 3b.iii, the gate driver IC accounts for 2 pF, and the transformer contributes 16 pF, see Fig. 3c. Thus, the total gate drive capacitance is  $C_{\rm GDC} = 18 \, \rm pF$ . In summary, the total parasitic switch-node capacitance of the half-bridge leg, Cpar, is the sum of the PCB ca-

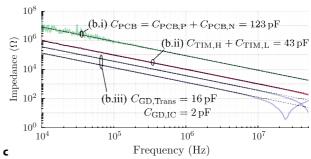

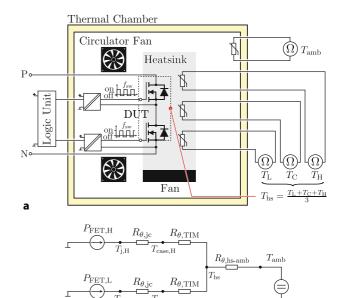

Fig. 4 a Measurement setup for the bridge-leg characterization, including three device-proximal temperature sensors  $T_L$ ,  $T_C$ , and  $T_H$ , one ambient sensor  $T_{amb}$ , and two circulator fans, ensuring a homogeneous temperature within the chamber. The device under test (DUT) is mounted on a heat sink with a high-temperature fan capable of adequate heat dissipation. **b** Equivalent thermal network circuit model. **c** Setup appearance with measurement instruments. Complete list of the instruments and accuracy is in Appendix

pacitance, one TIM capacitance, and one gate drive capacitance, yielding

$$C_{\text{par}} = C_{\text{PCB}} + C_{\text{TIM,L}} + C_{\text{GDC,H}} = 162.5 \,\text{pF}.$$

(1)

It should be noted that  $C_{\text{TIM,H}}$  and  $C_{\text{GDC,L}}$  do not affect the switch-node parasitic capacitance  $C_{\text{par}}$ , as the heatsink and the logic ground are connected to the negative DC-link rail.

#### 2.2 Measurement setup

To facilitate measurements under elevated ambient temperatures, the hardware demonstrator is placed within a thermal chamber capable of regulating the ambient temperature; see Fig. 4 and [43] for the details on the chamber. The constructed half-bridge PCB is mounted onto a heat sink, connected to PE for safety considerations, and equipped with a fan. In addition to the heatsink's fan, there are two circulator fans employed within the chamber to guarantee uniform temperature distribution. The inside of the thermal chamber is thermally isolated from outside, and the temperature is controlled by the function of the thermal chamber. It is essential to mention that the complete setup, including the fans, is designed to operate at high temperatures of up to 150 °C.

The selected cooling system has a low thermal resistance of  $R_{\theta,\text{hs-amb}} = 0.15 \text{ K/W}$ , thereby guaranteeing a minimal thermal gradient between the ambient temperature within the chamber and the heatsink, i.e.  $T_{\rm amb} \approx T_{\rm hs}$ . To derive the actual heat sink temperature, we take the average of the three employed sensors as shown in Fig. 4a, i.e.  $T_{hs} = (T_L + T_C + T_H)/3$ , which are affixed near the transistors using thermal epoxy [44]. Sil-Pad 2000 is employed as TIM [45], achieving a thermal resistance of around  $R_{\theta,\text{TIM}} = 0.92 \text{K/W}$  between the heat sink and the case of the power transistor. The device's junction-to-case thermal resistance is approximately equal to  $R_{\theta,jc} = 0.35 \text{ K/W}$  for the considered 20 mΩdevices. By employing a heatsink with a thermal resistance of 0.13 K/W [46], the majority of the heat flow occurs through the heatsink, and the thermal circuit network is depicted in Fig. 4b. Thus, the junction temperatures of the devices can be estimated based on the device losses  $P_{\text{FET,H}}$  and  $P_{\text{FET,L}}$ with

$$T_{j,H} = P_{\text{FET,H}} \left( R_{\theta,jc} + R_{\theta,\text{TIM}} \right) + T_{\text{hs}},$$

$$T_{j,L} = P_{\text{FET,L}} \left( R_{\theta,jc} + R_{\theta,\text{TIM}} \right) + T_{\text{hs}}.$$

(2)

Assuming the device losses in the high-side and low-side FETs are equal, i.e.,  $P_{\text{FET}} = P_{\text{FET,H}} = P_{\text{FET,L}}$ , the junction temperatures of the high-side and low-side FETs are also equal, resulting in  $T_{\text{j}} = T_{\text{j,H}} = T_{\text{j,L}}$ . It should be noted that  $R_{\theta,\text{TIM}}$  constitutes the majority of the thermal resistance due to its relatively larger value; therefore, minor differences between  $R_{\theta,\text{TIM}}$  due to different devices do not significantly impact the result. The desired junction temperature  $T_{\text{j}}$  required within the characterization can be achieved by changing the ambient temperature  $T_{\text{amb}} \approx T_{\text{hs}}$ , as

$$T_{\rm j} = P_{\rm FET} \left( R_{\theta,\rm jc} + R_{\theta,\rm TIM} \right) + T_{\rm hs},\tag{3}$$

assuming given device losses  $P_{\text{FET}}$ .

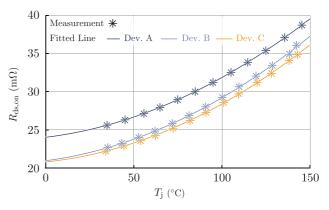

Fig. 5 Measured on-state resistance  $R_{\rm ds,on}$  of single device across junction temperature  $T_{\rm j}$  for Dev. A, Dev. B, and Dev. C. The results of the approximation (4) are shown with a continuous line, and the fitting coefficients are given in Table 2

#### 3 Bridge-leg characterization

Within this section, we present the measurement results across varying junction temperatures  $T_j$  and DC-link voltage  $V_{\rm DC}$  for on-state resistance  $R_{\rm ds,on}$ , output charge  $Q_{\rm oss}$  and gate charge  $Q_{\rm g}$ . From the gate charge we obtain Miller charge  $Q_{\rm M}=Q_{\rm g}-Q_{\rm g0}$  where  $Q_{\rm g0}=Q_{\rm g}(V_{\rm DC}=0)$ . We provide the measurements for the three considered MOSFETs.

#### 3.1 On-state resistance characterization

To characterize the relationship between on-state resistance  $R_{\rm ds,on}$  and junction temperature  $T_{\rm j}$ , we employed a thermal chamber to control the ambient temperature  $T_{\rm amb}$ . Once the desired thermal equilibrium was established, ensuring minimal disparity between the junction temperature  $T_{\rm j}$  and the heatsink temperature  $T_{\rm hs}$ , we take the measurement of the  $R_{\rm ds,on}$ . Keeping both transistors turned on and allowing a current of  $I_{\rm dc}=0.9$ A through them, we achieved a balance that minimized self-heating, thereby maintaining a negligible temperature difference between the heatsink and junction and ensured sufficient voltage drop for accurate  $V_{\rm DC}$  measurement. The on-state resistance results with  $R_{\rm ds,on}=\frac{1}{2}V_{\rm DC}/I_{\rm DC}$ .

Measurements were carried out across a temperature range from 30 °C to 150 °C for all three devices (Dev. A, Dev. B, and Dev. C), with the results shown in Fig. 5. It was observed that Dev. B and Dev. C exhibited nearly identical  $R_{\rm ds,on}$  values at room temperature, whereas Dev. A demonstrated a roughly 15% higher  $R_{\rm ds,on}$ . A notable increase in  $R_{\rm ds,on}$  was observed with rising junction temperatures  $T_{\rm j}$ , surging by over 50% at 150 °C. To accurately model the temperature dependency, a quadratic fit is employed as

$$R_{\rm ds,on}(T_{\rm j}) = \gamma_0 + \gamma_1 T_{\rm j} + \gamma_2 T_{\rm j}^2,$$

(4)

with the coefficients  $\gamma_0$ ,  $\gamma_1$ , and  $\gamma_2$  detailed in Table 2.

Tab. 2 Fitting coefficients for Dev. A, Dev B, and Dev. C

| Device | Coefficients for approximation |                            |                                      |                 |                |                      |               |              |  |

|--------|--------------------------------|----------------------------|--------------------------------------|-----------------|----------------|----------------------|---------------|--------------|--|

|        | $\gamma_0$ (m $\Omega$ )       | $\gamma_1$ (m $\Omega$ /K) | $\gamma_2~({\sf m}\Omega/{\sf K}^2)$ | $lpha_{ m oss}$ | $eta_{ m oss}$ | Q <sub>g0</sub> (nC) | $lpha_{ m g}$ | $eta_{ m g}$ |  |

| Dev. A | 24.02                          | 0.028                      | $5.05 \times 10^{-4}$                | 7.93            | 0.48           | 96.34                | 0.11          | 0.74         |  |

| Dev. B | 20.94                          | 0.030                      | $5.25 \times 10^{-4}$                | 8.82            | 0.49           | 156.49               | 0.34          | 0.54         |  |

| Dev. C | 20.78                          | 0.024                      | $5.27 \times 10^{-4}$                | 17.06           | 0.37           | 162.25               | 0.20          | 0.51         |  |

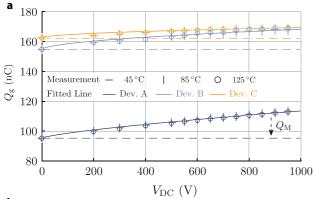

#### 3.2 Output charge characterization

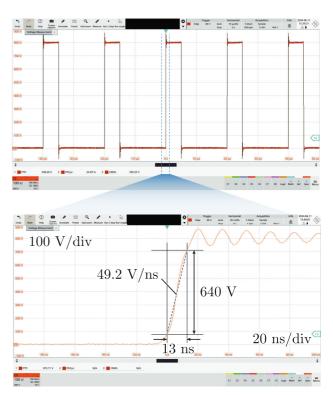

The characterization of the MOSFETs output charge  $Q_{\rm oss}$  is based on ZCS experiments [12, 47]. The switch node remains open, and the half-bridge operates at a predefined switching frequency  $f_{\rm sw}$  with a duty cycle of 25%, as shown in Fig. 10 for Dev. A. Upon switching on the transistor, the stored energy is dissipated as the  $C_{\rm oss}$  discharges from  $V_{\rm DC}$  to 0, while the  $C_{\rm oss}$  of the complementary device charges from 0 to  $V_{\rm DC}$ . Consequently, the DC supply needs to provide the associated bridge-leg losses given by

$$P_{\rm DC} = V_{\rm DC}I_{\rm DC} = V_{\rm DC} \left[ f_{\rm sw} \left( 2Q_{\rm oss} + C_{\rm par}V_{\rm DC} \right) + \frac{V_{\rm DC}}{R_{\rm disch}} \right], (5)$$

where a device-independent loss contribution is added by the discharge resistor  $R_{\rm disch}$  and parasitic capacitance  $C_{\rm par}$ , see **Sec.** 2.1. Finally, the output charge can be derived from the DC-link measurements with

$$Q_{\rm oss} = \frac{1}{2f_{\rm sw}} \left( I_{\rm DC} - \frac{V_{\rm DC}}{R_{\rm disch}} \right) - \frac{C_{\rm par}}{2} V_{\rm DC}. \tag{6}$$

To achieve the desired junction temperature  $T_{\rm j}$  for the experiments, the switching frequency  $f_{\rm sw}$  is adjusted to ensure each device dissipates 10 W, equating to  $V_{\rm DC}\,I_{\rm DC}-V_{\rm DC}^2/R_{\rm disch}=2P_{\rm FET}=20\,\rm W$ , which introduces a temperature difference of  $\Delta T=T_{\rm j}-T_{\rm hs}=13\,^{\circ}\rm C$  based on (3). This necessitates altering the  $f_{\rm sw}$  for each voltage level tested to maintain 10 W of dissipation, thereby setting the thermal chamber's temperature to

Fig. 6 Measured output charge  $Q_{\rm oss}$  of single device for Dev. A, Dev B, and Dev. C across DC-link voltage  $V_{\rm DC}$  under three junction temperature conditions  $T_{\rm j}=45\,^{\circ}{\rm C}$ ,  $85\,^{\circ}{\rm C}$ ,  $125\,^{\circ}{\rm C}$  to show temperature invariant characteristics. The results of the approximation (7) are shown with a continuous line, and the fitting coefficients are given in Table 2

$T_{\rm amb} = T_{\rm j} - \Delta T$ . For targeted junction temperatures of 45 °C, 85 °C, and 125 °C, this results in ambient temperatures of 32 °C, 72 °C, and 112 °C, respectively. The DC-link voltage was varied between 200 V and 950 V, leading to a switching frequency range between 30 kHz to 430 kHz.

The findings in Fig. 6 reveal the following conclusion:  $Q_{\rm oss}$  increases with voltage based on a non-linear relationship, as also shown in [48–50], but remains unaffected by junction temperature. Dev. A exhibited the lowest  $Q_{\rm oss}$ , consistent with its higher  $R_{\rm ds,on}$ , suggesting a smaller chip area compared to the other devices analyzed. At lower voltages, Dev. B and C showed marginally higher  $Q_{\rm oss}$  charges; Dev. B maintained this disparity across the voltage spectrum, whereas Dev. C's  $Q_{\rm oss}$  converged with Dev. A's at higher voltages. To quantitatively represent our data, we applied a curve fit to the output charge as

$$Q_{\rm oss}(V_{\rm DC}) = \alpha_{\rm oss} V_{\rm DC}^{\beta_{\rm oss}},\tag{7}$$

grounded in semiconductor physics [48–50], with coefficients  $\alpha_{\rm oss}$  and  $\beta_{\rm oss}$  detailed in Table 2.

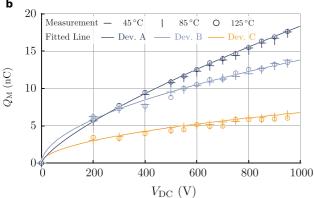

#### 3.3 Gate charge characterization

We utilized the same hardware configuration and operating points as in Sect. 3.2 to characterize the gate charge  $Q_g$ . The power demand of the gate driver comprising gate charge and gate driver losses and it can be obtained by  $P_{GD} = V_p I_p + V_n I_n$ , where the positive and negative gate supply voltages and currents  $V_p$ ,  $I_p$ ,  $V_{\rm n}$ , and  $I_{\rm n}$  are measured in situ, see Fig. 2. It is important to note that  $P_{\rm GD}$  depends on the switching frequency  $f_{sw}$ ; the faster the switching frequency, the higher the gate losses. However, even when the MOS-FET is not operated, i.e., when  $f_{sw} = 0$ , the gate driver IC consumes a certain baseline power  $P_{GD0}$  to supply its internal circuitry, which varies between 23 mW and 28 mW and must be measured for each ambient/ junction temperature. To estimate the gate charge  $Q_{\rm g}$ , the baseline power  $P_{\rm GD0}$  is subtracted from the  $P_{\rm GD}$ , which is measured for a given  $V_{DC}$  and a set  $f_{sw}$ . Therefore, the gate charge is calculated as

$$Q_{\rm g} = \frac{(P_{\rm GD} - P_{\rm GD0})/f_{\rm sw}}{V_{\rm g}},$$

(8)

where  $V_{\rm g} = V_{\rm p} - V_{\rm n} = 18.8 \, \rm V$  is consistently maintained throughout the experiments thanks to the voltage stabilizer integrated into the gate drive circuit.

Fig. 7 Measurement results for  $\bf a$  gate charge  $Q_{\rm g}$  and  $\bf b$  increase of the Miller charge  $Q_{\rm M}$  due to DC-link voltage of Dev. A, Dev B, and Dev. C across DC-link voltage  $V_{\rm DC}$  under three different junction temperatures 45 °C, 85 °C, 125 °C, showing temperature invariant characteristics. The results of the approximation (9) are plotted with a continuous line, and the fitting coefficients are given in Table 2

To quantify our measurement results, we fit the measurement data to

$$Q_{\rm g}(V_{\rm DC}) = Q_{\rm g0} + \alpha_g \, V_{\rm DC}^{\beta_g},$$

(9)

with coefficients provided in Table 2. The charge  $Q_{\rm g0}=Q_{\rm g}(0)$  represents the gate charge at zero DC-link voltage  $V_{\rm DC}=0$ , allowing for the estimation of the Miller charge as  $Q_{\rm M}=Q_{\rm g}-Q_{\rm g0}=\alpha_{\rm g}\,V_{\rm DC}^{\beta_{\rm g}}$ , depicted in Fig. 7b. These measurement results offer valuable insights into the performance of the studied transistors, showing that Dev. A possesses the lowest  $Q_{\rm g0}$ , which is advantageous for soft switching applications, suggesting its manufacturer has optimized the gate structure for SiC MOSFETs. Conversely,  $Q_{\rm M}$  of Dev. A exhibits the strongest dependency on  $V_{\rm DC}$  among all devices, whereas Dev. C shows the lowest  $V_{\rm DC}$  dependency. Dev. B and C display similar  $Q_{\rm g0}$  values, indicating subtle differences in their gate charge characteristics.

#### 4 Measurement-based figures of merit

Utilizing the measured data for on-state resistance  $R_{ds,on}$  versus junction temperature  $T_j$ , the gate charge

$Q_{\rm g0}$ , and the output charge  $Q_{\rm oss}$  and Miller charge  $Q_{\rm M}$  against DC-link voltage—affirmed to be independent of temperature—we obtained the FOMs listed in Table 1. Because  $R_{\rm ds,on}$  and charges  $Q_{\rm g0}$ ,  $Q_{\rm oss}$ ,  $Q_{\rm M}$  exhibit positive correlation with semiconductor device losses, i.e., conduction and switching losses, the characterized parameters shown in Table 2 are therefore positive correlation with the losses. Consequently, larger coefficients indicate higher losses and thus lower performance. These characterized parameters are substituted into the denominator of the respective FOMs, ensuring that larger FOM values correspond to lower losses and therefore higher performance.

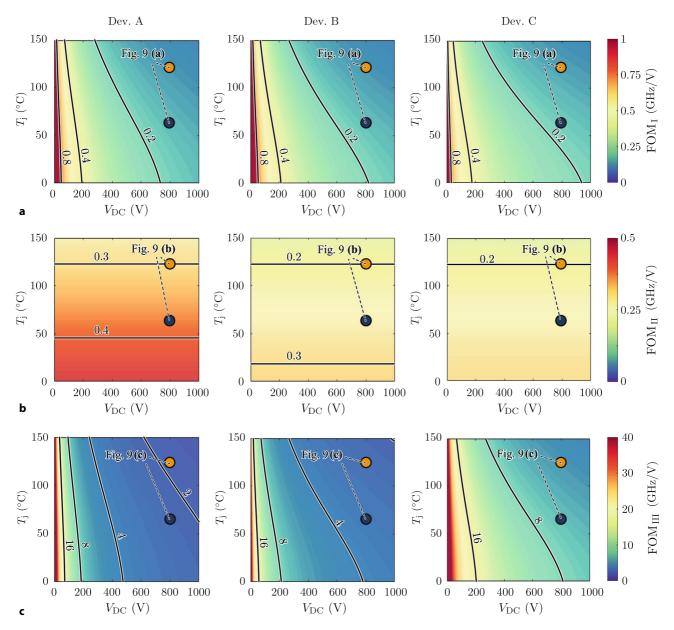

These FOMs are plotted against the DC-link voltage  $V_{DC}$  and junction temperature  $T_i$  to illustrate variations across different manufacturers, namely for Dev. A, B, and C, see Fig. 8. The analysis revealed that FOM<sub>I</sub> exhibits remarkable consistency across the measured devices. As  $FOM_I$  is defined using on  $Q_{oss}$ , consequently it indicates hard-switching losses [47]. Therefore, the results for FOM<sub>I</sub> suggest that SiC devices from various manufacturers can be replaced in hard-switched converters (with negligible overlap losses) without sacrificing performance. However, differences emerged for FOMII and FOMIII. For example, FOM<sub>II</sub> for Dev. A is approximately 33% higher than that for Dev. B and C. This discrepancy aligns with Dev. A's previously noted lower gate charge  $Q_{g0}$ (refer to Fig. 7a). Since FOM<sub>II</sub> is obtained using  $Q_{g0}$ , it consequently indicates the performance of devices operating under synchronous rectification, which underscores the need for thorough evaluation when considering second sourcing of associated power devices. Specifically, substituting Dev. A for Dev. B or C could increase losses and gate driver power. It should be noted that  $FOM_{II}$  is independent of  $V_{DC}$ as it is defined based on  $Q_{g0}$  that is measured for  $V_{\rm DC} = 0$ . Finally, as FOM<sub>III</sub> is defined using Miller charge  $Q_{\rm M}$ , it therefore indicates the performance of hard-switched converters where dv/dt associated loss components (overlap losses) are significant. A superior performance potential for Dev. C over Dev. A and B can be deduced from measurement-based FOMs. This finding suggests careful consideration when exploring second sourcing options for devices in converter systems with significant dv/dt switching loss component.

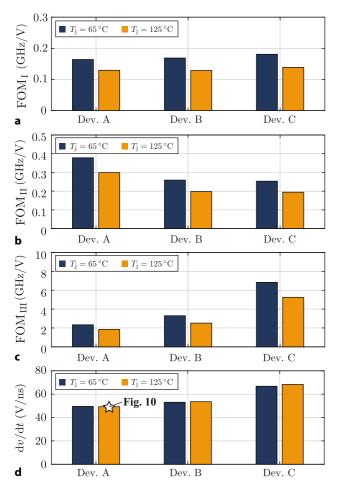

Fig. 9 reports results for a single operating point of  $V_{\rm DC} = 800\,\rm V$  and two different junction temperatures of  $T_{\rm j} = 65\,^{\circ}\rm C$  and  $T_{\rm j} = 125\,^{\circ}\rm C$ . As discussed for Fig. 8, there is a consistency over devices for FOM<sub>I</sub>, whereas for FOM<sub>II</sub> or FOM<sub>III</sub>, either Dev. A or Dev. C perform the best. In addition, we provide dv/dt measurements in Fig. 9d for the same operating points, which are obtained as indicated in Fig. 10 using *Rohde & Schwarz MXO 5* oscilloscope and passive probe *RT-ZL04*. The dv/dt values match the trend of FOM<sub>III</sub>, justifying its relation to overlap losses.

Fig. 8 Figures of Merit (FOMs) obtained from measurement results of  $R_{ds,on}$ ,  $Q_{oss}$ ,  $Q_{g0}$  and  $Q_{M}$  for Dev. A, B, and C across junction temperature  $T_{j}$  and DC-link voltage  $V_{DC}$ : **a** FOM<sub>II</sub> and **c** FOM<sub>III</sub>. See Table 1 for the definition of the FOMs

#### 5 Conclusions

This paper offers a detailed, measurement-driven analysis of Silicon Carbide (SiC) devices from three distinct manufacturers designated as Dev. A, B, and C. The primary aim of this study is to provide design engineers with comparative insights into the performance of SiC devices across various manufacturers, assessing the implications of second sourcing on design complexity. To facilitate this evaluation, we have developed a high-temperature experimental setup capable of characterizing TO-247-4 packaged DUTs, enabling us to compare the measured onstate resistance  $R_{\rm ds,on}$ , output charge  $Q_{\rm oss}$ , and gate charge  $Q_{\rm g}$ , under constant (load-independent) gate drive voltages. The devices were characterized at

temperatures up to 150 °C for  $R_{\rm ds,on}$  and up to 125 °C for  $Q_{\rm oss}$  and  $Q_{\rm g}$ . With these measurements, we empirically show the temperature independence of the charges  $Q_{\rm oss}$  and  $Q_{\rm g}$ . Further, utilizing the measured data for  $R_{\rm ds,on}$ ,  $Q_{\rm oss}$ , and  $Q_{\rm g}$ , we construct Figures of Merit (FOMs) as a function of DC-link voltage  $V_{\rm DC}$  and junction temperature  $T_{\rm j}$ . Our findings reveal that an FOM indicating the performance of a hard-switched converter system (with negligible overlap losses) has minimal disparities between devices. However, gate charge-based FOMs vary substantially, underscoring the critical importance when selecting SiC devices for synchronous rectification or in high-current operation, causing substantial overlap losses, as also verified by  ${\rm d}v/{\rm d}t$  measurements.

Fig. 9 Comparison of a FOM<sub>II</sub>, b FOM<sub>II</sub>, c FOM<sub>III</sub> and d  ${\rm d} \, v/{\rm d} \, t$ , for the operating point where  $V_{\rm DC} = 800\,{\rm V}$  at two different junction temperatures  $T_{\rm j} = 65\,{\rm ^{\circ}C}$  and  $T_{\rm j} = 125\,{\rm ^{\circ}C}$

Our future research will focus on thermal characterization of bridge-legs including overlap losses and development of rapid power semiconductor loss evaluation methods based on switching transients,  $\mathrm{d}v/\mathrm{d}t$  behavior, and transient waveform analysis.

**Funding** Open access funding provided by University of Innsbruck and Medical University of Innsbruck.

Open Access Dieser Artikel wird unter der Creative Commons Namensnennung 4.0 International Lizenz veröffentlicht, welche die Nutzung, Vervielfältigung, Bearbeitung, Verbreitung und Wiedergabe in jeglichem Medium und Format erlaubt, sofern Sie den/die ursprünglichen Autor(en) und die Quelle ordnungsgemäß nennen, einen Link zur Creative Commons Lizenz beifügen und angeben, ob Änderungen vorgenommen wurden. Die in diesem Artikel enthaltenen Bilder und sonstiges Drittmaterial unterliegen ebenfalls der genannten Creative Commons Lizenz, sofern sich aus der Abbildungslegende nichts anderes ergibt. Sofern das betreffende Material nicht unter der genannten Creative Commons Lizenz steht und die betreffende Handlung nicht nach gesetzlichen Vorschriften erlaubt ist, ist für die oben aufgeführten Weiterverwendungen des Materials die Einwilligung des jeweiligen Rechteinhabers einzuholen. Weitere Details zur

Fig. 10 Switch node voltage measurement in ZCS operation. The  ${\rm d}v/{\rm d}t$  is approximated assuming a linear voltage rise from 10% to 90% of the DC link voltage. The shown measurement corresponds to Dev. A operating at  $V_{\rm DC}=800{\rm V},\ f_{\rm sw}=50{\rm\,kHz}$  and a duty cycle of 0.25

Lizenz entnehmen Sie bitte der Lizenzinformation auf http://creativecommons.org/licenses/by/4.0/deed.de.

### 6 Appendix: Measurement instruments and error control

This appendix describes the measurement equipment and error control used for the characterizations.

#### 6.1 Temperature measurement

Throughout the whole characterization process, TE Connectivity CLASS AA RTD PT1000 was utilized as a temperature sensor. The resistance  $R_{\rm m}$  of the sensor was measured using digital multi meter (DMM) Brymen 869s, and the measured temperature  $T_{\rm m}$  was obtained using the RTD conversion formula in the case  $T_{\rm m} > 0[51]$ :

$$T_{\rm m} = \frac{-R_0 a + \sqrt{(R_0 a)^2 - 4R_0 b(R_0 - R_{\rm m})}}{2R_0 a},$$

(10)

where  $a = 3.9083 \times 10^{-3}$ ,  $b = -5.775 \times 10^{-7}$  and  $R_0 = 1000 \Omega$ . According to the datasheet [51], the measurement error of the RTD itself is expressed as

$$\Delta T_{\text{m,RTD}} = \pm (0.1 + 0.0017 \times T_{\text{m}}).$$

(11)

The error of the DMM is represented by the error propagation using (10) as

$$\Delta T_{\rm m,DMM} = \pm \left| \frac{\partial T_{\rm m}}{\partial R_{\rm m}} (R_{\rm m}) \right| \Delta R_{\rm m},$$

(12)

where  $\Delta R_{\rm m}$  consists of a reading error of 0.07% Rdg. and a full scale error of 0.2  $\Omega$ , and can be derived from the general form of the measurement error:

$$\Delta X_{\rm m} = \text{F.S.} + \text{Rdg.} \times X_{\rm m},\tag{13}$$

where  $X_{\rm m}$  is generalized measured parameter. The errors of  $\Delta T_{\rm m,RTD}$  and  $\Delta T_{\rm m,DMM}$  are calculated as follows. First, measured  $R_{\rm m}$  is substituted into (10), from which we obtain  $T_{\rm m}$ . Then,  $T_{\rm m}$  is substituted into (11) to derive  $\Delta T_{\rm m,RTD}$ .  $\Delta T_{\rm m,DMM}$  are calculated by substituting  $R_{\rm m}$  and  $\Delta R_{\rm m}$  into (12), which finally leads to total error as

$$\Delta T_{\rm m} = \Delta T_{\rm m,RTD} + \Delta T_{\rm m,DMM},\tag{14}$$

with the highest measurement temperature of 150 °C corresponding to  $\Delta T_{\rm m} = \pm 0.69$  °C, and the lowest measurement temperature of 30 °C corresponding to  $\Delta T_{\rm m} = \pm 0.20$  °C.

#### 6.2 R<sub>ds,on</sub> measurement

For the measurement of  $R_{\rm ds,on}$ , the voltage and the current over the DUT were measured using a high precision digital multi meter GW Instek GDM 9060. During characterization, the voltage range can be fixed at 100 mV and the current range at 1A according to the characterization procedures. The voltage measurement error  $\Delta V_{\rm m}$  is 0.009% Rdg.+0.0065% F.S. and the current measurement error  $\Delta I_{\rm m}$  is 0.1% Rdg.+0.01% F.S. under the measurement condition[52]. Since measured value  $R_{\rm ds,on,m}$  was calculated as

$$R_{\rm ds,on,m} = \frac{V_{\rm m}}{I_{\rm m}},\tag{15}$$

the total error of  $R_{ds,on}$  is estimated as

$$\Delta R_{\rm ds,on,m} = \pm \left| \frac{\partial R_{\rm ds,on,m}}{\partial V_{\rm m}} (V_{\rm m}, I_{\rm m}) \right| \Delta V_{\rm m}$$

$$\pm \left| \frac{\partial R_{\rm ds,on,m}}{\partial I_{\rm m}} (V_{\rm m}, I_{\rm m}) \right| \Delta I_{\rm m}, \tag{16}$$

where  $\Delta V_m$  and  $\Delta I_m$  are calculated by (13). The calculated maximum measurement error of  $\pm 0.05\, \text{m}\Omega$ at the temperature of 150 °C resulting in that the deviation from the fitting curve is hardly observable in Fig. 5 due to this level of precision.

#### 6.3 $Q_{oss}$ , $Q_g$ and $Q_M$ measurement

For the characterization of each charge  $Q_{\rm oss}, Q_{\rm g}$  and  $Q_{\rm M}$ , the voltage and current of the half-bridge were measured using the voltage module U7005 with

0.02% Rdg.+0.03% F.S. and current sensor *CT6872* with 0.05% Rdg.+0.0202% F.S. of the power analyzer *HIOKI PW8001*[53]. To ensure measurement accuracy, the current sensor was wound with a measurement wire eight times. Additionally, the switching frequency was measured using spectrum analyzer function of oscilloscope *Rohde & Schwarz MXO 5*.

As described in Sect. 3.2 and Sect. 3.3, the characterization of each charge is performed by dividing the power consumption, obtained from the half-bridge DC bus voltage and current measurements, by the switching frequency. For the same power consumption, an increase in switching frequency reduces the energy consumed per switching cycle, However, the error rate should remain constant. Thus, we assume that the measured switching frequency is the true value without error and calculate the relative error excluding the frequency. The frequency measurement accuracy of the oscilloscope  $\Delta f_{\rm sw,m}$  is  $0.02\,{\rm ppm}\times f_{\rm sw,m}+1.1\,{\rm \mu Hz}$ , resulting in a charge error  $\Delta Q=\left|\frac{\partial Q}{\partial f_{\rm sw,m}}\right|\Delta f_{\rm sw,m}<0.001\,{\rm nC}$ , which is negligible and supports the aforementioned assumption.

In the characterization of  $Q_{oss}$ , the indirect measurement parameters are denoted as

$$x_{\rm m} = [V_{\rm DC,m}, I_{\rm DC,m}, V_{\rm disch,m}, I_{\rm disch,m}, C_{\rm par,m}]. \tag{17}$$

The relative measurement error of  $\Delta Q_{\rm oss}/Q_{\rm oss}$  is expressed as

$$\frac{\Delta Q_{\text{oss}}}{Q_{\text{oss}}} = \frac{\frac{1}{2f_{\text{sw,m}}} |\Delta f(x_{\text{m}})| + |\Delta g(x_{\text{m}})|}{\frac{1}{2f_{\text{sw,m}}} f(x_{\text{m}}) + g(x_{\text{m}})},$$

(18)

where f and g correspond to the functions derived from (6) as

$$f(x_{\rm m}) = I_{\rm DC,m} - \frac{V_{\rm DC,m}}{V_{\rm disch,m}/I_{\rm disch,m}},$$

(19)

$$g(x_{\rm m}) = -V_{\rm DC,m}C_{\rm par,m}/2.$$

(20)

The errors associated with these functions  $\Delta f$  and  $\Delta g$ , are given by

$$\Delta f(x_{\rm m}) = \sum_{i=1}^{5} \left| \frac{\partial f}{\partial x_{\rm m,i}}(x_{\rm m}) \right| \Delta x_{\rm m,i},\tag{21}$$

$$\Delta g(x_{\rm m}) = \sum_{i=1}^{5} \left| \frac{\partial g}{\partial x_{\rm m,i}}(x_{\rm m}) \right| \Delta x_{\rm m,i},\tag{22}$$

where

$$\Delta x_{\rm m} = [\Delta V_{\rm DC,m}, \Delta I_{\rm DC,m}, \Delta V_{\rm disch,m}, \Delta I_{\rm disch,m}, \Delta C_{\rm par,m}]. \eqno(23)$$

$\Delta C_{\rm par} = \pm 0.1\,{\rm pF}$  is substituted as the least significant digit of the  $C_{\rm par}$  measurement, and other parameters of  $\Delta x_{\rm m}$  are derived by (13) according to the range settings of the power analyzer.

As a result of the above calculations, the maximum relative error of  $Q_{\rm oss}$  is 2.3% at a voltage of 950V corresponding to  $\pm 5.4\,\rm nC$ . The relative error of  $Q_{\rm g}$  and  $Q_{\rm M}$  can be derived in same manner, resulting in the maximum relative error is 0.66% at voltage of 950V corresponding to  $\pm 1.1\,\rm nC$ . Due to these errors, measurement variance can be observed in Fig. 7b for  $Q_{\rm M}$  which has a smallest range of 20 nC, while for  $Q_{\rm oss}$  and  $Q_{\rm g}$ , the variance from the fitted curve is hardly noticeable in Fig. 6 and 7a since their errors are small relative to their ranges.

#### References

- Jones EA, Wang FF, Costinett D (2016) Review of commercial GaN power devices and GaN-based converter design challenges. IEEE J Emerg Sel Topics Power Electron 4(3):707–719. https://doi.org/10.1109/JESTPE.2016. 2582685

- Östling M, Ghandi R, Zetterling C-M (2011) SiC power devices — present status, applications and future perspective. In: Proc. of the IEEE 23rd International Symposium on Power Semiconductor Devices and ICs (ISPSD 2011). San Diego, CA, USA https://doi.org/10.1109/ISPSD.2011. 5890778

- 3. Elasser A, Chow TP (2002) Silicon carbide benefits and advantages for power electronics circuits and systems. Proc Ieee 90(6):969–986. https://doi.org/10.1109/JPROC.2002. 1021562

- 4. Pittini R, Zhang Z, Andersen MAE Switching performance evaluation of commercial SiC power devices (SiC JFET and SiC mosfet) in relation to the gate driver complexity. In: Proc. of the IEEE Energy Conversion Congress and Expo Asia Downunder (ECCE Asia 2013). Melbourne, VIC, Australia, In https://doi.org/10.1109/ECCE-Asia.2013.6579102

- 5. Tu H, Feng H, Srdic S, Lukic S (2011) Extreme fast charging of electric vehicles: A technology overview. Ieee Trans Transportation Electrification 5(4):861–878. https://doi.org/10.1109/TTE.2019.2958709

- Ohno T, Mirić S, Guillod T, Krismer F, Huber J, Kolar JW (2023) New triple-output quad-active-bridge DC/DC converter employing a four-leg inverter input stage. In: Proc. of the 26th International Conference on Electrical Machines and Systems (ICEMS 2023). Zhuhai, Guangdong, China https:// doi.org/10.1109/ICEMS59686.2023.10344769

- Menzi D, Weihe S, Anderson JA, Everts J, Kolar JW (2022) Single-Phase PFC rectifier with integrated flying capacitor power pulsation buffer. Ieee Open J Power Electron 3:866–875. https://doi.org/10.1109/OJPEL.2022.3221679

- Zhang F, Ma X, Huang L, Xu P, Xuan Y, Yang X, Hao X, Li Z (2017) Design and demonstration of a SiC-based 800-V/10-kV1-MWSolid-State transformer for Grid-Connected photovoltaic systems. In: Proc. of the IEEE 3rd International Future Energy Electronics Conference (IFEEC 2017). Kaohsiung, Taiwan https://doi.org/10.1109/IFEEC. 2017.7992355

- Menzi D, Kolar JW, Sarnago H, Lucía Ó, Huber JE (2023) New 600V GaN single-stage isolated bidirectional 400V input three-phase PFC rectifier. In: Proc. of the IEEE Energy Conversion Congress and Exposition (ECCE 2023). Nashvill, TN, USA https://doi.org/10.1109/ECCE53617.2023.10362864

- Rothmund D, Guillod T, Bortis D, Kolar JW (2019) 99.1% efficient 10 kV SiC-based medium-voltage ZVS bidirectional single-phase PFC AC/DC stage. IEEE J Emerg Sel Topics

- Power Electron 7(2):779–797. https://doi.org/10.1109/ JESTPE.2018.2886140

- 11. Jahns TM, Dai H (2017) The past, present, and future of power electronics integration technology in motor drives. Cpss Trans Power Electron Appl 2(3):197–216. https://doi.org/10.24295/CPSSTPEA.2017.00019

- 12. Haider M, Fuchs S, Zulauf G, Bortis D, Kolar JW, Ono Y (2022) Analytical loss model for three-phase 1200V SiC MOS-FET inverter drive system utilizing miller capacitor-based dv/dt-limitation. Ieee Open J Power Electron 3:93–104. https://doi.org/10.1109/OJPEL.2022.3143995

- 13. Elrajoubi AM, Ang SS, George K (2019) Design and analysis of a new GaN-based AC/DC converter for battery charging application. IEEE Trans on Ind Applicat 55(4):4044–4052. https://doi.org/10.1109/TIA.2019.2915687

- 14. Li B, Li Q, Lee FC, Liu Z, Yang Y (2018) A high-efficiency high-density wide-bandgap device-based bidirectional on-board charger. IEEE J Emerg Sel Topics Power Electron 6(3):1627–1636. https://doi.org/10.1109/JESTPE. 2018.2845846

- 15. Nguyen HV, Lee D-C, Blaabjerg F (2021) A novel SiC-based multifunctional onboard battery charger for plug-in electric vehicles. Ieee Trans Power Electron 36(5):5635–5646. https://doi.org/10.1109/TPEL.2020.3026034

- 16. Reimers J, Dorn-Gomba L, Mak C, Emadi A (2019) Automotive traction inverters: Current status and future trends. IEEE Trans Veh Technol 68(4):3337–3350. https://doi.org/10.1109/TVT.2019.2897899

- 17. Huang AQ (2016) Wide bandgap (WBG) power devices and their impacts on power delivery systems. In: Proc. of the IEEE International Electron Devices Meeting (IEDM 2016). IEEE, San Francisco, USA

- $18.\ Beaurenaut\,L\,(2018)\,SiC-based\,power\,modules\,cut\,costs\,for\\battery-powered\,vehicles.\,Power\,Electron\,Eur\,3:22-25$

- 19. Zhang H, Tolbert LM, Ozpineci B (2010) Impact of SiC devices on hybrid electric and plug-in hybrid electric vehicles. IEEE Trans on Ind Applicat 47(2):912–921

- Zhang D, Cao D, Huber J, Everts J, Kolar JW (2023) Non-isolated three-phase current DC-link buck-boost EV charger with virtual output midpoint grounding and ground current control. IEEE Transactions on Transportation Electrification https://doi.org/10.1109/TTE.2023.3282978

- 21. Ohno T, Hoshi N (2022) Current tracking control of triple active bridge DC/DC converter under varying DC-bus voltage conditions. Ieee Open J Power Electron 3:834–845. https://doi.org/10.1109/OJPEL.2022.3218283

- Haider M, Anderson JA, Mirić S, Nain N, Zulauf G, Kolar JW, Xu D, Deboy G (2020) Novel ZVS S-TCM modulation of three-phase AC/DC converters. Ieee Open J Power Electron 1:529–543. https://doi.org/10.1109/OJPEL.2020.3040036

- 23. Okada R, Ota R, Hoshi N (2022) Soft-switching converter for inductive power transfer system with double-sided LCC resonant network. In: Proc. of the 24th European Conference on Power Electronics and Applications (EPE 2022-ECCE Europe)

- 24. Sayed MA, Suzuki K, Takeshita T, Kitagawa W (2017) Soft-switching PWM technique for grid-tie isolated bidirectional DC–AC converter with SiC device. IEEE Trans on Ind Applicat 53(6):5602–5614. https://doi.org/10.1109/TIA. 2017.2731738

- 25. Research GV Silicon Carbide Semiconductor Devices Market Size, Share, & Trends Analysis Report By Component, By Product, by Wafer Size, By End-use, By Region, And Segment Forecasts, 2022 2030. https://www.grandviewresearch.com/industry-analysis/silicon-carbide-semiconductor-devices-market-report

- 26. Johnson E (1965) Physical limitations on frequency and power parameters of transistors. In: Proc. of the 1958 IRE International Convention Record, vol 13. https://doi.org/10.1109/IRECON.1965.1147520

- 27. Keyes RW (1972) Figure of merit for semiconductors for high-speed switches. Proc Ieee 60(2):225–225. https://doi.org/10.1109/PROC.1972.8593

- 28. Baliga BJ (1982) Semiconductors for high-voltage, vertical channel field-effect transistors. J Appl Phys 53(3):1759–1764. https://doi.org/10.1063/1.331646

- 29. Brown J, Moxey G (1989) Power MOSFET basics: Understanding MOSFET characteristics associated with the figure of merit. Ieee Electron Device Lett 10(10)

- 30. Kim JJ, Park J-H, Sabri S, Fetzer B, Hull B, Ryu S-H (2024) Investigation into Relationship of the Switching Performance and Short-Circuit Withstand Time on 1.2 kV 4H-SiC Power MOSFETs. In: Proc. of the IEEE International Symposium on Power Semiconductor Devices and ICs (ISPSD 2024). IEEE, In, pp 148–151

- 31. Chee AK (2022) On the design principles of 3-D RESURFenhanced RF SOI LDMOSFETs: Gate geometry optimization and rescaling. IEEE Trans Electron Devices 69(12):6523–6528

- 32. Sung W, Han K, Baliga B (2017) Optimization of the JFET region of 1.2 kV SiC MOSFETs for improved high frequency figure of merit (HF-FOM). In: Proc. of the IEEE Workshop on Wide Bandgap Power Devices and Applications (WiPDA 2017). IEEE, pp 238–241

- 33. Han K, Baliga B (2019) Comparison of four cell topologies for 1.2-kV accumulation-and inversion-channel 4H-SiC MOSFETs: Analysis and experimental results. IEEE Trans Electron Devices 66(5):2321–2326

- 34. Kim I-J, Matsumoto S, Sakai T, Yachi T (1995) New power device figure of merit for high-frequency applications. In: Proc. of the International Symposium on Power Semiconductor Devices and ICs (ISPSD 1995). Yokohama, Japan https://doi.org/10.1109/ISPSD.1995.515055

- 35. Baliga BJ (1989) Power semiconductor device figure of merit for high-frequency applications. Ieee Electron Device Lett 10(10):455–457. https://doi.org/10.1109/55.43098

- 36. Huang AQ (2004) New unipolar switching power device figures of merit. Ieee Electron Device Lett 25(5):298–301. https://doi.org/10.1109/LED.2004.826533

- 37. DiMarino C, Chen Z, Danilovic M, Boroyevich D, Burgos R, Mattavelli P (2013) High-temperature characterization and comparison of 1.2 kV SiC power MOSFETs. In: Proc. of the IEEE Energy Conversion Congress and Exposition (ECCE 2013). IEEE, pp 3235–3242

- 38. Ravi L, Severson EL, Tewari S, Mohan N (2014) Circuit-level characterization and loss modeling of SiC-based power electronic converters. In: Proc. of the IEEE Industrial Electronics Society (IECON 2014). IEEE, pp 1291–1297

- 39. Semiconductor Corporation O SiC MOSFETs: Gate Drive Optimization. https://www.onsemi.com/pub/collateral/tnd6237-d.pdf

- 40. Haider M, Niklaus PS, Madlener M, Rohner G, Kolar JW (2023) Comparative evaluation of gate driver and LC-filter based dv/dt-limitation for SiC-based motor-integrated variable speed drive inverters. Ieee Open J Power Electron 4:450–462. https://doi.org/10.1109/OJPEL.2023.3283052

- 41. Infineon Technologies 1EDI60N12AF 1200 V single-channel gate driver with separate output and short circuit clamping. https://www.infineon.com/cms/en/product/power/gate-driver-ics/ledi60n12af/

- 42. Infineon Technologies The TLE4251D a monolithic integrated low drop voltage tracker in the very small SMD package PG-TO252-5-1. https://www.infineon.com/cms/en/

- product/power/linear-voltage-regulator/linear-voltage-regulators-for-automotive-applications/tle4251d/

- 43. BINDER Model ED 56 | Drying and heating chambers with natural convection. https://www.binder-world.com/int-en/products/drying-and-heating/product/ed-56

- 44. CHIP QUIK AD1-10S. https://www.chipquik.com/datasheets/AD1-10S.pdf

- 45. Bergquist Company BERGQUIST SIL PAD TSP 3500. https://www.henkel-adhesives.com/at/en/product/ther mal-sil-pad-materials/bergquist\_sil\_padtsp3500

- 46. Fischerelektronik Cooling aggregates with axial fan LA 21 150 24. https://www.fischerelektronik.de/web\_fischer/en\_GB/heatsinks/D04/Cooling%20aggregates%20with%20axial%20fan/VA/LA2115024/index.xhtml

- 47. Azurza Anderson J, Zulauf G, Kolar JW, Deboy G (2020) New figure-of-merit combining semiconductor and multi-level converter properties. Ieee Open J Power Electron 1:322–338. https://doi.org/10.1109/OJPEL.2020.3018220

- 48. Kasper M, Burkart RM, Deboy G, Kolar JW (2016) ZVS of power MOSFETs revisited. Ieee Trans Power Electron 31(12):8063–8067. https://doi.org/10.1109/TPEL. 2016.2574998

- 49. Costinett D, Maksimovic D, Zane R (2015) Circuit-oriented treatment of nonlinear capacitances in switched-mode power supplies. Ieee Trans Power Electron 30(2):985–995. https://doi.org/10.1109/TPEL.2014.2313611

- 50. Kolar JW, Krismer F, Lobsiger Y, Muhlethaler J, Nussbaumer T, Minibock J (2012) Extreme efficiency power electronics. In: Proc. of the 7th International Conference on Integrated Power Electronics Systems (CIPS 2012). Nuremberg, Germany

- 51. TE CONNECTIVITY RTD Temperature Sensors. https://www.te.com/en/products/sensors/temperature-sensors/rtd-sensors-and-probes.html

- 52. GW Instek GDM-906x Dual Measurement Multimeter. https://www.gwinstek.com/en-global/products/detail/ GDM-906x

- 53. HIOKI POWER ANALYZER PW8001. https://www.hioki. com/global/products/power-meters/power-analyzer/id\_ 412384

**Publisher's Note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Takanobu Ohno,** received his B.Sc., M.Sc., and Ph.D. in electrical engineering from Tokyo University of Science, Japan, in 2018, 2020, and 2022, respectively. From 2022 to 2023, he was a visiting researcher at the Power Electronic Systems Laboratory, Swiss Federal Institute of Technology (ETH) Zurich, Switzerland. In 2023, he joined the Innsbruck Drives and Energy Systems Laboratory at the University of Innsbruck, Austria, where he is currently a Postdoctoral Researcher in the Department of Mechatronics. His research interests include control and modulation for power electronics and drive systems.

**Michael Haider,** received his M.Sc. and Ph.D. in electrical engineering from the Swiss Federal Institute of Technology (ETH) Zurich, Switzerland, in 2017 and 2022, respectively. In 2017, he joined the Power Electronic Systems Laboratory at ETH Zurich as a Ph.D. student, focusing on motor-integrated power factor corrected single-to-three-phase AC/AC converter concepts. His research interests include synergetically controlled two-stage systems, soft-switching converter topologies, widebandgap power semiconductor devices, and their application in next-generation variable speed drive systems.

**Spasoje Mirić**, received his B.Sc., M.Sc., and Ph.D. in electrical engineering from the University of Belgrade, School of Electrical Engineering, in 2012, 2013, and 2018, respectively, with a focus on power electronics systems and drives. In 2021, he defended his second Ph.D. thesis at ETH Zurich, specializing in advanced mechatronic systems. His research during this Ph.D. centered on linear-rotary actuator systems with magnetic bearings, resulting in two new machine topologies that have been patented.

Since 2021, Dr. Mirić has been a postdoctoral researcher at ETH Zurich, where his research included wide- bandgap (WBG) power converter optimization with both hard and soft-switching, wireless power transfer systems, and eddy-current-based position sensor systems. In 2023, Dr. Mirić was appointed Assistant Professor and Head of the Innsbruck Drives and Energy Systems Laboratory at the University of Innsbruck (UIBK).

Dr. Mirić has authored over 40 scientific papers in international journals and conference proceedings and holds seven patents. He has presented three educational seminars at leading international conferences and has received five IEEE Transactions and Conference Prize Paper Awards.